CMOS逆向工程:苏联老式计数器芯片为例

我最近发现了一张有趣的苏联 1 芯片裸片照片,该芯片可能设计于 20 世纪 70 年代。本文以该芯片为例,介绍 CMOS 电路逆向工程的入门指南。虽然这块芯片乍看起来像一团乱麻,但其庞大的功能和简单的布局使我们有可能理解它的电路。首先,我将解释如何识别单个晶体管。一组组晶体管以标准模式连接,构成 CMOS 栅极、多路复用器、触发器和其他电路。一旦了解了这些构件,逆向工程整个芯片就变得切实可行了。该芯片原来是一个 4 位 CMOS 计数器,是摩托罗拉 MC14516B 的复制品。

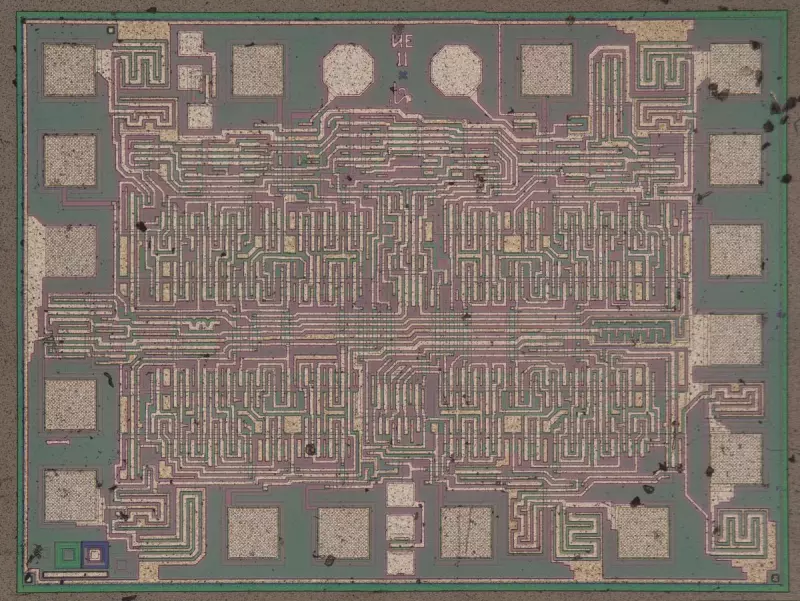

晶片上的К561ИЕ11 芯片的芯片照片。图片由 Martin Evtimov 提供。点击此图片(或其他图片)查看大图。

上图是显微镜下的微型硅芯片。硅的各个区域都掺入了杂质,以改变硅的电气特性。这种掺杂还能使硅的各个区域呈现绿色或红色,具体取决于某个区域的掺杂方式。(在硅的顶部,可以看到白色的金属层,形成芯片的连接。这种芯片使用的是金属栅极晶体管,这是一种古老的技术,因此金属层也构成了晶体管的栅极。在芯片外围,16 个方形键合焊盘将芯片与外界连接起来。安装到封装中时,芯片在焊盘和引线框架(连接芯片引脚的金属结构)之间有微小的键合线。

根据俄罗斯的数据表2 ,芯片有 319 个 “元件”,这应该是指半导体器件。芯片还有少量二极管用于保护输入,因此晶体管总数略高于 300 个。当然,与拥有数百亿晶体管的现代 CMOS 处理器相比,这个晶体管数量根本不算什么,但大部分电路原理是相同的。

NMOS 和 PMOS 晶体管

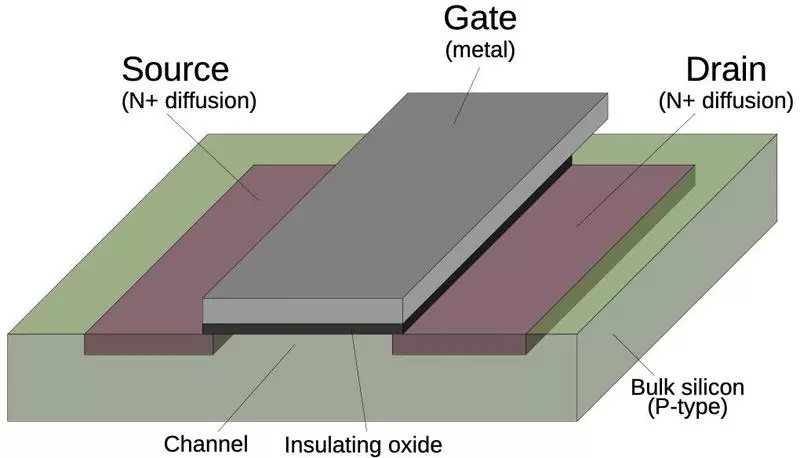

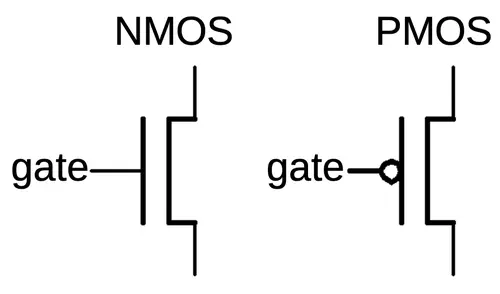

CMOS(互补 MOS)电路使用两种类型的晶体管(NMOS 和 PMOS)共同工作。下图显示了 NMOS 晶体管的构造。晶体管可视为源极和漏极之间的开关,由栅极控制。源极和漏极区域(红色)由掺杂杂质的硅组成,以改变其半导体特性,形成 N+ 硅。栅极由铝层组成,与硅之间隔着一层很薄的绝缘氧化物层4 (这三层–金属、氧化物、半导体–是 MOS 晶体管名称的由来)。氧化层是绝缘体,因此基本上没有电流通过栅极,这也是 CMOS 成为低功耗技术的原因之一。然而,薄薄的氧化层很容易被静电破坏,因此 MOS 集成电路对静电放电很敏感。

NMOS 晶体管的结构

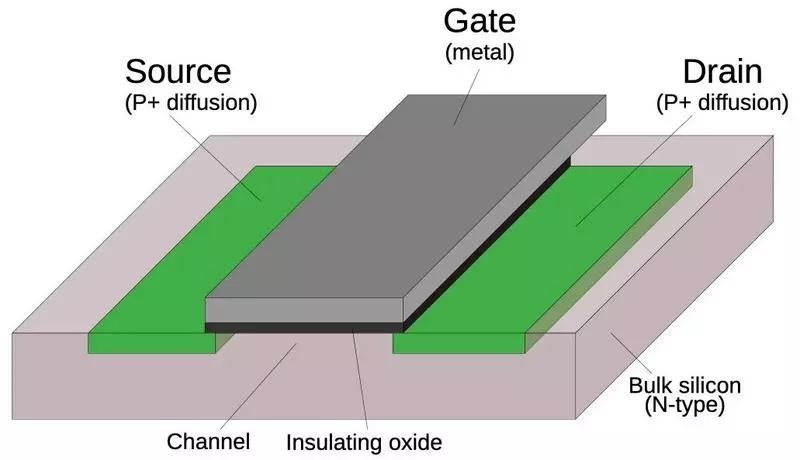

PMOS 晶体管(下图)的结构与 NMOS 晶体管正好相反:源极和漏极被掺杂以形成 P+ 区域,而底层的大块硅则是 N 型硅。掺杂过程非常有趣,但我将在脚注中详细介绍5。

PMOS 晶体管的结构。

NMOS 和 PMOS 晶体管的结构和工作方式相反;这就是 CMOS 中的 “互补”。NMOS 晶体管在栅极为高电平时导通,而 PMOS 晶体管在栅极为低电平时导通。NMOS 晶体管最擅长将输出拉低,而 PMOS 晶体管最擅长将输出拉高。在 CMOS 电路中,晶体管协同工作,根据需要将输出拉高或拉低。MOS 晶体管的行为非常复杂,因此本文对其进行了简化,只需了解数字电路即可。

如果您从电子产品供应商处购买 MOS 晶体管,它的包装上有三根引线,分别用于源极、栅极和漏极。源极和漏极在封装内的连接方式不同,在电路中不能互换。但在集成电路中,晶体管是对称的,源极和漏极是相同的。因此,在下面的讨论中,我将不再区分源极和漏极。我将在下文中使用对称符号来表示 NMOS 和 PMOS 晶体管;PMOS 栅极上的反相气泡表示低信号激活 PMOS 晶体管。

NMOS 和 PMOS 晶体管的符号。

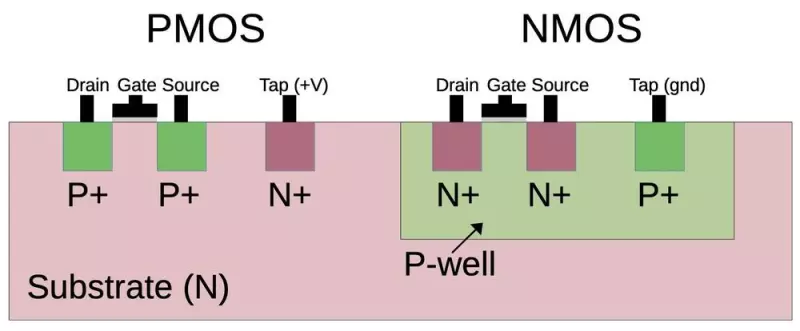

一个复杂的问题是,NMOS 晶体管是在 P 型硅上制造的,而 PMOS 晶体管是在 N 型硅上制造的。由于硅芯片本身是 N 型硅,因此 NMOS 晶体管周围需要有一个 P 型硅盆或硅井6。下图的横截面图显示了右侧的 NMOS 晶体管是如何嵌入 P 型硅井中的。构造两种具有相反行为的晶体管会使制造变得更加复杂,这也是 CMOS 多年后才流行起来的原因之一。CMOS 于 1963 年在飞兆半导体公司(Fairchild Semiconductor)发明,但 RCA 是 CMOS 的主要倡导者,并于 20 世纪 60 年代末将其商业化。尽管 RCA 在 1974 年就生产出了 CMOS 微处理器,但主流微处理器直到 20 世纪 80 年代中期才开始转用 CMOS,推出了摩托罗拉 68020(1984 年)和英特尔 386(1986 年)等芯片。

CMOS 晶体管的横截面。

对于 PMOS 晶体管,衬底通过抽头与电源相连,而对于 NMOS 晶体管,阱区通过抽头与地相连7 。在逆向工程中,抽头可提供重要线索,显示哪些区域是 NMOS,哪些是 PMOS。正如下文所述,这些电压对于理解该芯片的电路也非常重要。

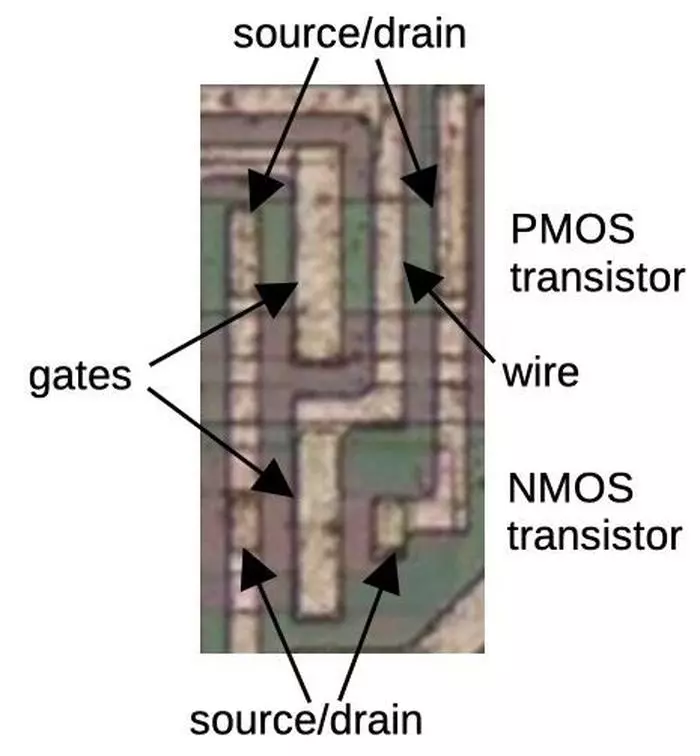

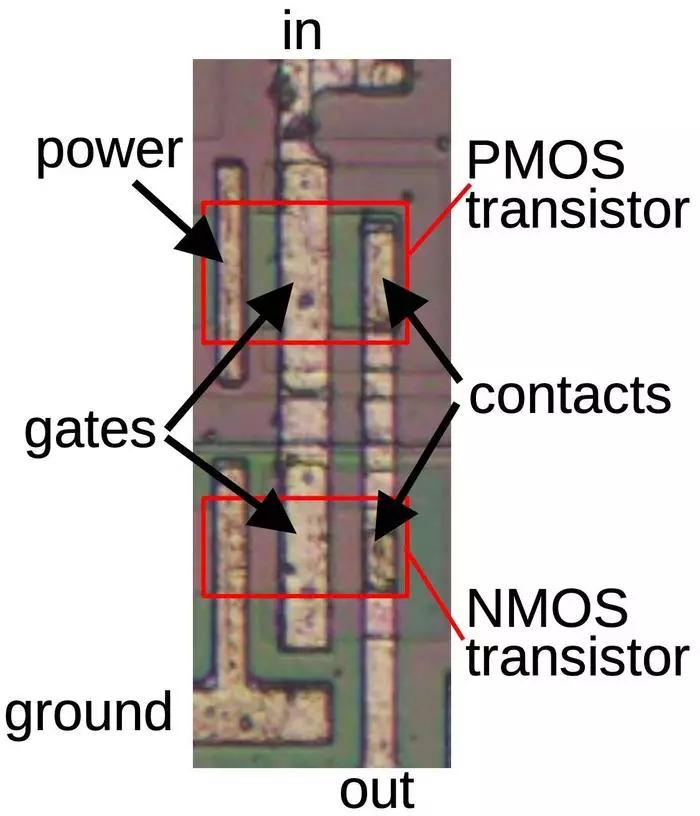

下面的芯片照片显示了芯片上的两个晶体管。不同集成电路的晶体管外观各不相同,因此逆向工程的第一步就是确定它们在特定芯片中的外观。在这个集成电路中,晶体管栅极可以通过硅片上的一个大矩形区域来区分。(在其他金属栅极晶体管中,栅极通常呈 “气泡 “状。在大多数情况下,金属线穿过硅,被厚厚的绝缘氧化物隔离。金属和硅之间的接触面是一个较小的椭圆形区域,颜色略深;金属线与下面的晶体管源极和漏极相连。MOS 晶体管通常没有分立的边界;正如稍后将看到的,一个晶体管的源极可能与另一个晶体管的漏极重叠。

芯片上有两个晶体管

区分 PMOS 和 NMOS 晶体管可能比较困难。在该芯片上,P 型硅呈现绿色,N 型硅呈现红色。因此,PMOS 晶体管显示为绿色区域被红色包围,而 NMOS 则相反。此外,PMOS 晶体管通常比 NMOS 晶体管大,因为它们的强度较弱。区分它们的另一种方法是看它们在电路中的连接。如下所示,逻辑门中的 PMOS 晶体管与电源相连,而 NMOS 晶体管与地相连。

金属栅极晶体管是一种非常古老的技术,在 20 世纪 70 年代大多被硅栅极晶体管所取代。硅栅极电路使用额外的多晶硅布线层。此外,现代集成电路通常有不止一层金属。本文章中的金属栅极集成电路比现代集成电路更容易理解,因为需要分析的层数更少。现代集成电路的 CMOS 原理是相同的,但布局会有所不同。

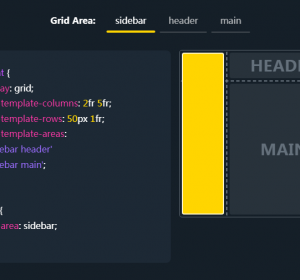

在 CMOS 中实现反相器

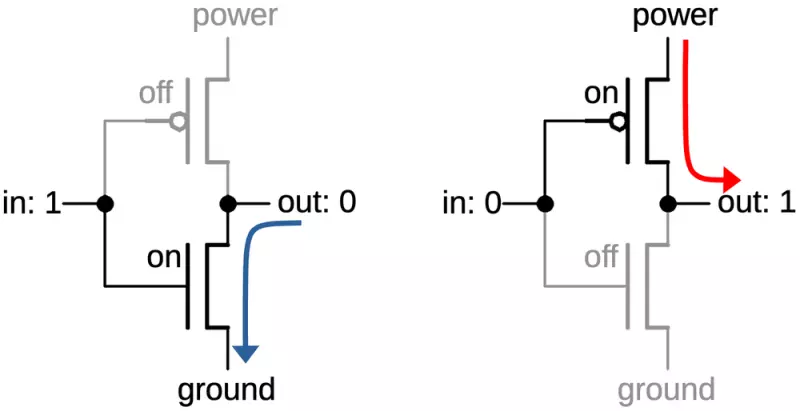

最简单的 CMOS 栅极是一个反相器,如下图所示。虽然是最基本的,但它说明了 CMOS 电路的大部分原理。反相器由顶部的 PMOS 晶体管和底部的 NMOS 晶体管构成,前者将输出拉高,后者将输出拉低。输入端与两个晶体管的栅极相连。

CMOS 反相器由一个 PMOS 晶体管(上)和一个 NMOS 晶体管(下)构成。

回想一下,NMOS 晶体管是通过栅极上的高电平信号导通的,而 PMOS 晶体管则相反,是通过低电平信号导通的。因此,当输入高电平时,NMOS 晶体管(底部)导通,将输出拉低。当输入低电平时,PMOS 晶体管(顶部)导通,将输出拉高。请注意晶体管是如何以相反(即互补)的方式工作的。

逆变器的功能

芯片上的反相器如下所示。PMOS 和 NMOS 晶体管用红色方框表示,晶体管的连接方式如上图所示。输入端与两个晶体管的栅极相连,栅极为较大的金属矩形。右侧的两个触点将晶体管的漏极连接到输出端。电源和地线的连接与大多数芯片有些不同,因为金属线似乎并不通向任何地方。标有 “电源 “的短金属线将 PMOS 晶体管的源极与衬底(晶体管周围的红色硅)相连。如前所述,基板与芯片电源相连。因此,晶体管通过衬底硅接收电源。由于硅的电阻相对较高,这种方法并不理想,但它简化了布线。同样,接地金属将 NMOS 晶体管的源极与环绕晶体管的 P 型硅井(呈绿色)相连。井接地后,晶体管就有了接地连接。

芯片上的逆变器

有些逆变器与上面的布局不同。许多芯片的反相器都是两个反相器并联,以提供两倍的输出电流。下图显示的是一个双反相器,它基本上是前一个反相器的镜像和复制,顶部是两个 PMOS 晶体管,底部是两个 NMOS 晶体管。请注意,成对晶体管之间没有明确的边界;它们的漏极共享同一个硅片。因此,每个输出触点都由两个晶体管共享,而不是复制。

由两个并联逆变器组成的逆变器。

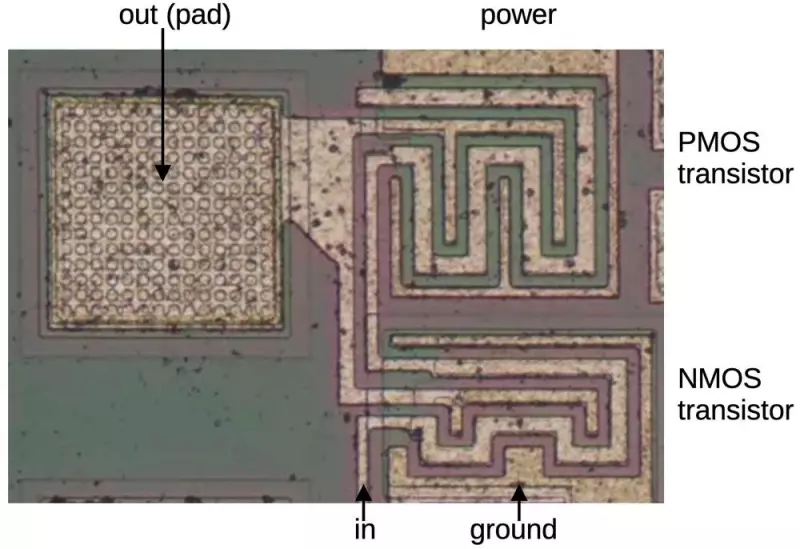

另一种反相器驱动芯片的输出引脚。输出引脚需要大电流来驱动外部电路。芯片使用大得多的晶体管来提供这种电流。尽管如此,输出驱动器仍使用前面所述的相同反相器电路,用一个 PMOS 晶体管将输出置高,用一个 NMOS 晶体管将输出拉低。下图显示了芯片上的一个输出反相器。为了在可用空间内安装较大的晶体管,晶体管采用蛇形布局,栅极绕组位于源极和漏极之间。反相器的输出端连接到一个键合垫。当芯片安装在封装中时,细小的键合线将焊盘与外部引脚连接起来。

输出驱动器是一种反相器,使用更大的晶体管。

NOR 和 NAND 逻辑门

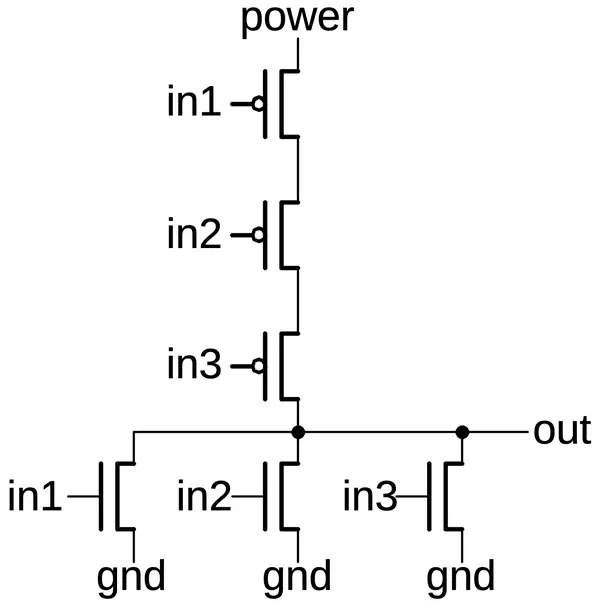

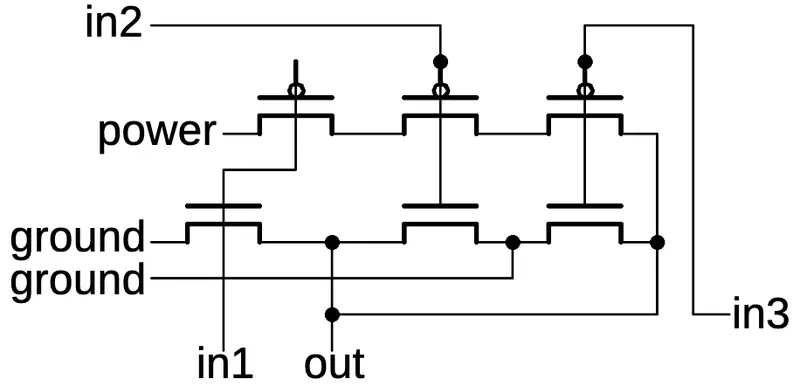

其他逻辑门的构造概念与反相器相同,只是多了一些晶体管。在 NOR 逻辑门中,顶部的 PMOS 晶体管是串联的,因此如果所有输入均为 0,输出将被拉高;底部的 NMOS 晶体管是并联的,因此如果任何输入为 1,输出将被拉低。请再次注意互补作用:PMOS 晶体管将输出拉高,而 NMOS 晶体管将输出拉低。此外,PMOS 晶体管是串联的,而 NMOS 晶体管是并联的。下面的电路是一个三输入 NOR 门,同样支持不同数量的输入。(只有一个输入时,电路会变成一个反相器,正如你所预期的那样)。

CMOS 实现的 3 输入 NOR 门。

对于任何栅极实现,输入必须要么被 PMOS 端拉高,要么被 NMOS 端拉低。如果某些输入同时出现这两种情况,电源和地线就会短路,可能会毁坏芯片。如果这两种情况都没有发生,输出将是浮动的,这在 CMOS 电路中是不好的。9 在上面的 NOR 栅极中,您可以看到对于任何输入,输出总是按要求被拉高或拉低。逆向工程提示:如果输出不是始终为高电平或低电平,则可能是 PMOS 电路或 NMOS 电路出错了10。

下图显示了 3 输入 NOR 栅极在芯片上的显示方式。11 晶体管栅极是厚厚的垂直金属矩形;PMOS 晶体管在上,NMOS 在下。三个 PMOS 晶体管串联在左边的电源和右边的输出连接之间。与反相器一样,电源和接地连接线与硅块相连,而不是与芯片的电源线和地线相连。

在芯片上实现的 3 输入 NOR 栅极。左边 “额外 “的 PMOS 晶体管是另一个门的一部分。

NMOS 晶体管的布局更为复杂,因为仅用一层金属很难将晶体管并联起来。输出线连接第一个和第二个晶体管以及第三个晶体管。一个与众不同的特点是,第二和第三个 NMOS 晶体管与地的连接是通过一条水平的掺杂硅线完成的(虚线所示的红色 “硅路径”)。这条硅线从接地金属延伸到两个晶体管之间的区域。最后,请注意 PMOS 晶体管要比 NMOS 晶体管大得多。这既是因为 PMOS 晶体管本身的效率较低,也是因为串联的晶体管需要较低的电阻,以免降低输出信号的质量。逆向工程提示:通常比较容易识别串联的晶体管,然后利用该信息确定哪些晶体管必须并联。

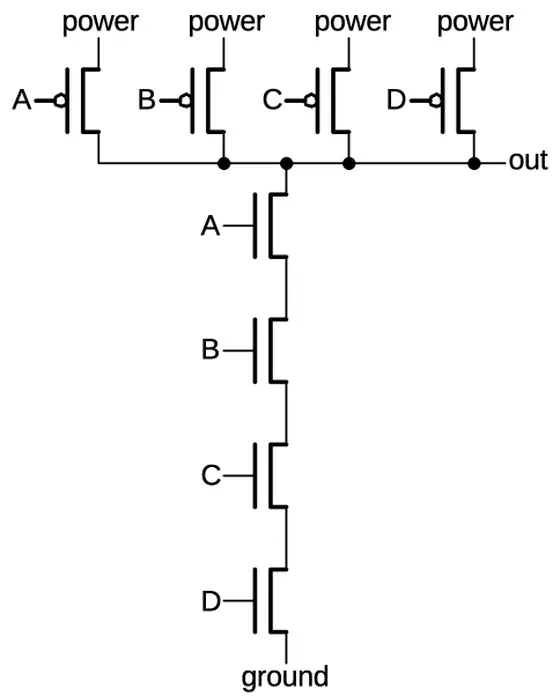

NAND 栅极是通过调换串联和并联晶体管的角色来实现的。也就是说,PMOS 晶体管是并联的,而 NMOS 晶体管是串联的。例如,下面的原理图显示了一个 4 输入 NAND 栅极。如果所有输入均为 1,NMOS 晶体管将把输出拉低。如果任何输入为 0,则相应的 PMOS 晶体管会将输出拉高。这样,电路就实现了 NAND 功能。

CMOS 实现的 4 输入 NAND 栅极。

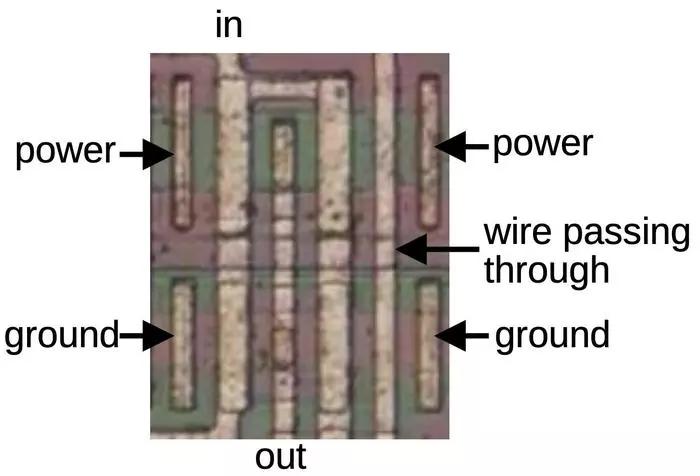

下图显示了芯片上的一个四输入 NAND 栅极。在下半部分,四个 NMOS 晶体管串联,而在上半部分,四个 PMOS 晶体管并联。(请注意,与 NOR 栅极相比,串联和并联晶体管是开关式的)。与 NOR 栅极一样,电源和地线由与硅块的金属连接提供(电源有两个连接)。并联 PMOS 电路使用 “硅通路”(绿色)将每个晶体管连接到输出端,而不会与金属相交。中间的硅片顶部有一条垂直的金属线;这样可以降低硅通路的电阻。在这种情况下,NMOS 晶体管比 PMOS 晶体管大,因为 NMOS 晶体管是串联的。

芯片上的四输入 NAND 栅极。

复杂门电路

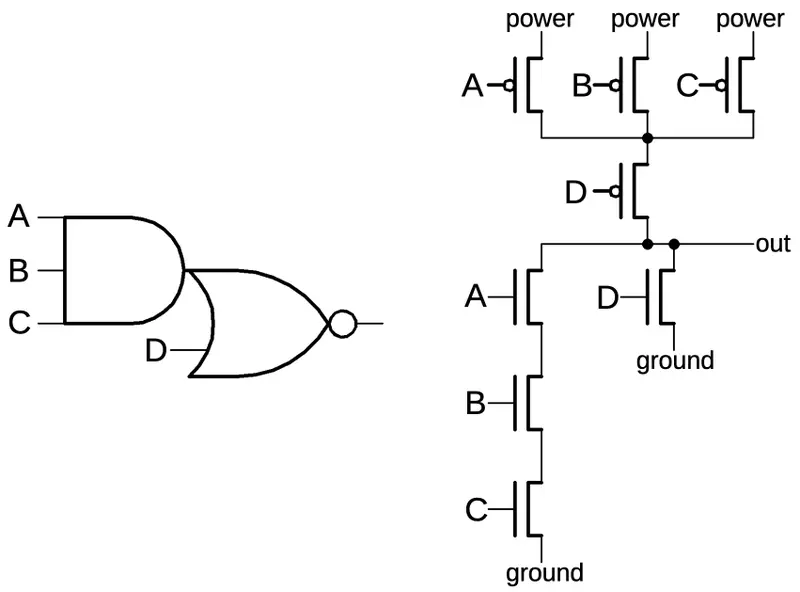

更复杂的门,如 AND-NOR(AND-OR-INVERT),也可以用 CMOS 制作;这些门之所以常用,是因为它们并不比 NAND 或 NOR 门更难制作。下面的原理图显示了一个 AND-NOR 门。要了解其结构,请查看通过 NMOS 晶体管的接地路径。第一条路径是通过 A、B 和 C。如果这些输入端均为高电平,则输出端为低电平,从而实现该门的 AND-INVERT 端。第二条路径是通过 D,它本身会将输出拉低,从而实现栅极的 OR-INVERT 端。您可以验证 PMOS 晶体管是否在必要的情况下将输出拉高。请注意,D 晶体管在 PMOS 侧是串联的,而在 NMOS 侧是并联的,这再次显示了这些电路的互补性。

一个 AND-NOR 门。

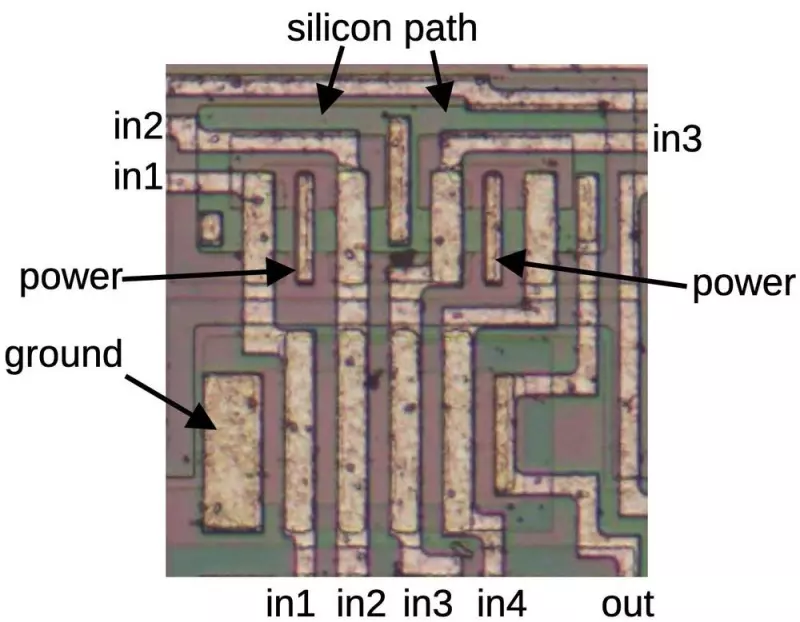

下图显示了芯片上的 AND-NOR 门,四个输入端 A、B、C 和 D 与上图原理图相对应。这个门具有一些棘手的布局特点。最令人吃惊的是,在这个门的中间有另一个门(一个 3 输入 NOR 门)的一半。另一个门的输出(D)是我们正在研究的这个门的输入。忽略另一个栅极,AND-NOR 栅极的 NMOS 晶体管位于第一列的红色条带上方,PMOS 晶体管位于第三列的绿色条带上方。与上面的原理图一致,左边有三个串联的 NMOS 晶体管,分别连接到 A、B 和 C,D 晶体管在接地和输出之间提供了第二条通路。在 PMOS 端,A、B 和 C 晶体管并联,然后通过 D 晶体管连接到输出端。右侧绿色的 “硅通路 “提供了从晶体管 A 和 B 到晶体管 C 和 D 的并联连接。但为了穿过导线 B 和 C,金属在绿色硅片提供连接的地方出现了断裂。

芯片上的 AND-NOR 栅极

与其他栅极一样,电源也是通过与大块硅的连接获得的,连接红色和绿色区域。如果仔细观察,会发现有一条绿色带(”硅通路”)从电源连接处向下延伸,连接到 B 和 C 晶体管之间的主绿色区域,通过硅为这些晶体管提供电源。另一方面,NMOS 晶体管的顶部和底部都有接地连接。在此电路中,接地是通过顶部和底部的实心金属线提供的,而不是与硅块连接。

在对逻辑门进行逆向工程时,有几条原则很有帮助。首先,由于 CMOS 的互补性,输出必须由 PMOS 晶体管拉高或由 NMOS 晶体管拉低。因此,每一个可能的输入都必须激活一组或另一组。这意味着相同的输入必须同时进入 NMOS 和 PMOS 晶体管。此外,NMOS 和 PMOS 电路的结构是互补的:NMOS 晶体管并联时,PMOS 晶体管必须串联,反之亦然。在上述 AND-NOR 电路中,这些原理都很有用。例如,您可能不会发现 “硅通路”,但由于 PMOS 的一半必须与 NMOS 的一半互补,因此您知道这些连接必须存在。

即使是复杂的栅极,也可以通过将 NMOS 晶体管分成串联和并联两组(对应于 AND 和 OR 项)来反向设计。请注意,MOS 晶体管本质上是反相的,因此单个栅极总是以反相结束。因此,您可以构建一个 AND-OR-AND-NOR 逻辑门,但您无法将一个 AND 逻辑门构建为单个电路。

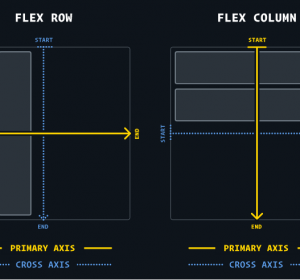

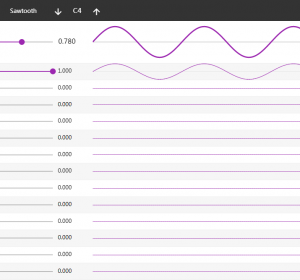

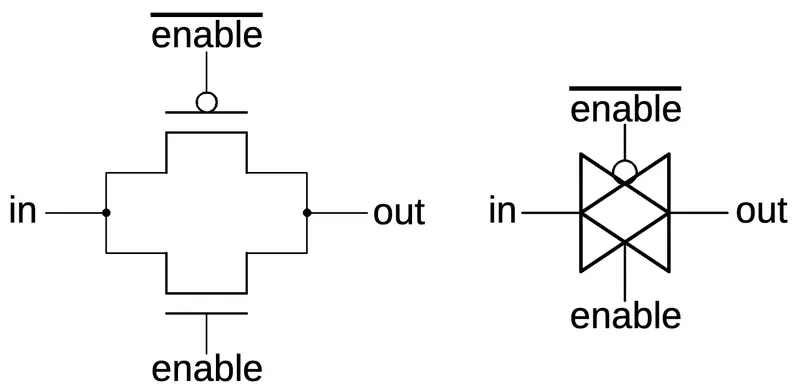

传输门

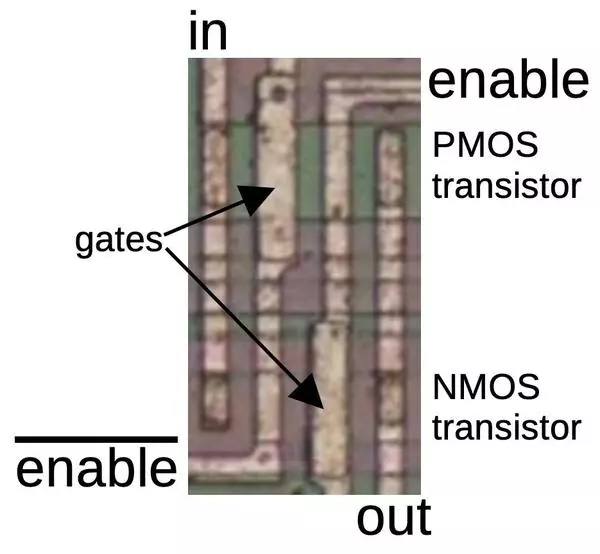

另一个关键电路是传输门。它起着开关的作用,可以通过信号,也可以阻断信号。下面的原理图显示了传输门是如何由两个晶体管(一个 NMOS 晶体管和一个 PMOS 晶体管)构成的。如果使能线为高电平(即 PMOS 晶体管为低电平),两个晶体管都会导通,将输入信号传递到输出端。NMOS 晶体管主要传递低电平信号,而 PMOS 晶体管则传递高电平信号,因此它们协同工作。如果使能线为低电平,则两个晶体管都会关闭,从而阻断输入信号。传输门的原理符号如右图所示。请注意,传输门是双向的,它没有特定的输入和输出。通过检查周围的电路,通常可以看出哪一侧是输入,哪一侧是输出。

一个传输栅极由两个晶体管构成。图中标出了晶体管及其栅极。右侧为原理图符号。

下图显示了芯片上的传输栅极。它由顶部的 PMOS 晶体管和底部的 NMOS 晶体管组成。使能信号和互补使能信号都被使用,一个用于 NMOS 晶体管的栅极,另一个用于 PMOS 晶体管。

芯片上的传输栅极,由两个晶体管组成。

逆变器和传输门都是双晶体管电路,但在逆向工程中很容易区分。其中一个区别是,反相器连接电源和地线,而传输门则不连接电源。此外,反相器只有一个输入端,而传输门有三个输入端(包括控制线)。在反相器中,两个晶体管栅极具有相同的输入端,因此一次只开启一个晶体管。而在传输门中,两个栅极的输入端相反,因此晶体管同时开启或关闭。

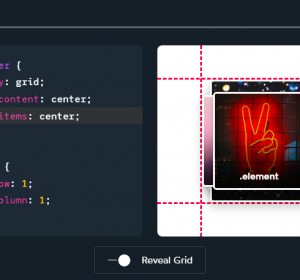

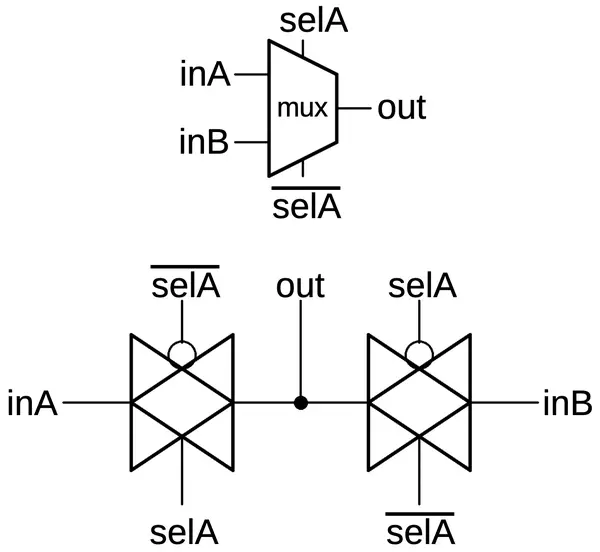

多路复用器是一种有用的电路,它可以从两个(或多个)输入端中选择一个。下面的多路复用器选择输入端 inA 或 inB,并根据选择线 selA 的高电平或低电平分别将其连接到输出端。如图所示,该多路复用器可由两个传输门构成。请注意,第二个传输门上的选择线是翻转的,因此一次只能激活一个传输门。通过使用更多的传输门和额外的选择线,可以构建具有更多输入端的多路复用器。

一个多路复用器的示意图及其两个传输门的实现。

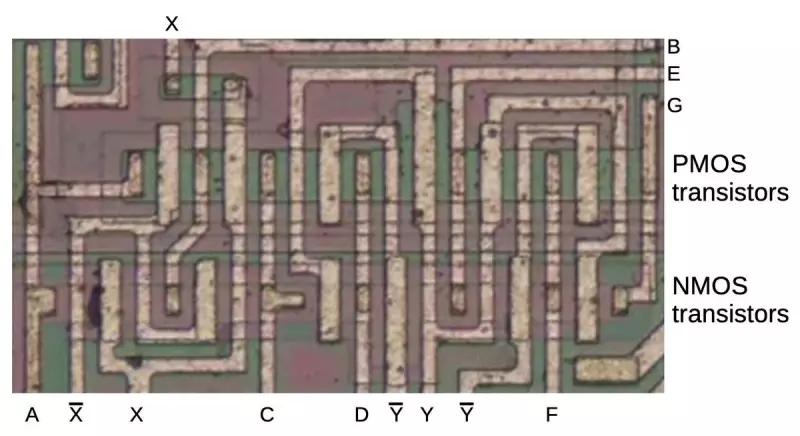

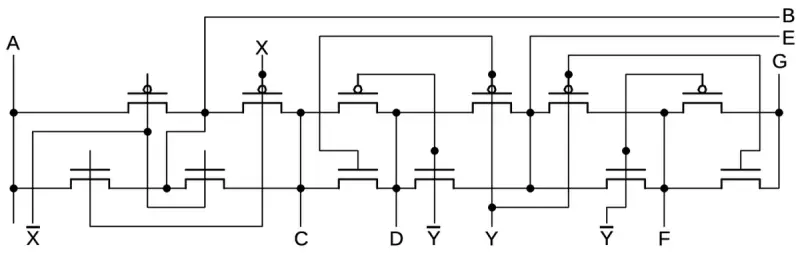

下面的芯片照片显示的是由六个 PMOS 晶体管和六个 NMOS 晶体管组成的传输栅极块。随着逆向工程的深入,金属线上的标签将变得更有意义。请注意,金属层提供了电路的大部分布线,但不是全部。大部分布线是隐含的,即相邻晶体管的连接是因为一个晶体管的源极与另一个晶体管的漏极重叠。

实现多个传输栅极的晶体管块。

虽然这看起来像一块难以理解的 “之 “字形线块,但描画出晶体管就能看到电路(如下图)。原理图中的布线与芯片上的物理布局一致,因此原理图有点乱。由于只有一层金属用于布线,为了避免电线交叉,布局变得有些复杂。(本图中唯一的交叉线位于左上方的 X 线;信号使用一小段硅片从金属下通过)。

前一组晶体管的示意图。

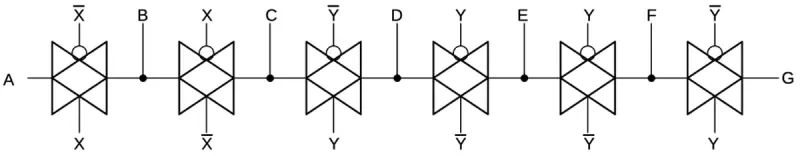

将 PMOS 和 NMOS 晶体管看成一对,就会发现上面的电路是一连串的传输门(如下图所示)。虽然不能立即看出哪些线是输入线,哪些线是输出线,但可以猜测,使用相反控制线的成对传输门构成了一个多路复用器。也就是说,输入端 A 和 C 复用到输出端 B,输入端 C 和 E 复用到输出端 D,以此类推。正如我们将看到的,这些传输门组成的多路复用器是触发器的一部分。

晶体管构成六个传输门。

锁存器和触发器

触发器和锁存器是重要的电路,能够保持一个位并由时钟信号控制。术语并不统一,但我会用触发器来指边缘触发器件,用锁存器来指电平触发器件。也就是说,触发器会在时钟信号变为高电平的瞬间(即使用时钟边沿)抓取其输入,将其存储起来并作为输出提供,由于历史原因,我们称之为 Q。而锁存器则会在时钟信号为高电平时(即使用时钟电平)抓取输入、存储并输出。锁存器被认为是 “透明 “的,因为只要时钟为高电平,输入就会立即显示在输出上。

锁存器和触发器之间的区别看似迂腐,实则重要。触发器可预测地在每个时钟周期更新一次,而锁存器只要时钟处于高电平就会不断更新。通过反相器将触发器的输出端连接回输入端,就可以创建一个切换触发器,它将在每个时钟周期翻转一次状态,将时钟除以二。(如果用透明锁存器做同样的事情,就会产生振荡:输出一旦翻转,就会反馈到锁存器输入端并再次翻转。

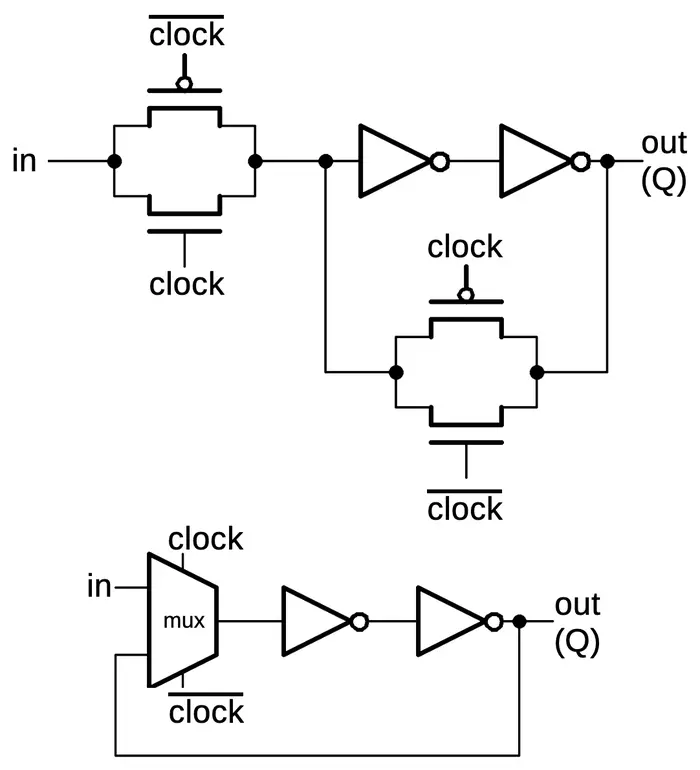

下面的原理图显示了如何利用传输门实现锁存器。当时钟为高电平时,第一个传输门将输入传递到反相器和输出。当时钟为低电平时,第二个传输门为反相器建立反馈回路,使其保持其值,从而实现锁存功能。下图是使用多路复用器绘制的相同电路,可能更容易理解:反相器选择输入或反馈。

由传输门实现的锁存器。下图显示了带有多路复用器的相同电路。

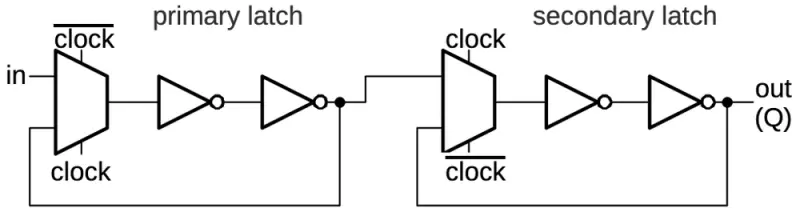

通过将两个锁存器以主/副排列的方式组合在一起,可以创建一个边缘触发的触发式触发器。当时钟为低电平时,输入将进入主锁存器。当时钟切换到高电平时,会发生两件事。主锁存器将保持输入的当前值。与此同时,次级锁存器将开始将其输入(来自初级锁存器的值)传递到输出,进而传递到触发器的输出。其效果是,触发器的输出将是时钟变高时的值,触发器对其他时间的变化不敏感。(当时钟处于低电平时,主锁存器的值会不断变化,但这不会影响触发器的输出)。

两个锁存器,组合成一个触发器。

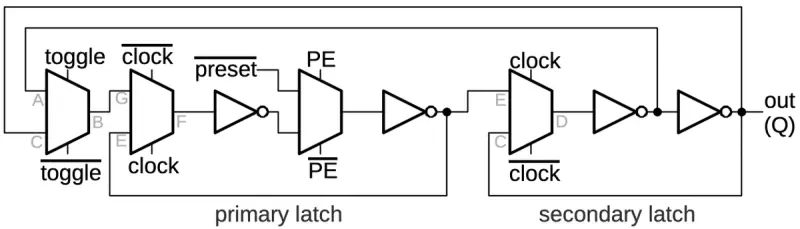

计数器芯片中的触发器以上述设计为基础,但具有两个额外的功能。首先,在预置使能(PE)信号的控制下,触发器可以加载一个值。其次,在切换 (T) 信号的控制下,触发器可以保持当前值或切换其值。实现这些功能需要在主锁存器中增加两个多路复用器,如下图所示。第一个多路复用器选择将反相输出或非反相输出反馈到触发器,从而提供可选择的切换动作。第二个多路复用器是锁存器的标准时钟多路复用器。第三个多路复用器可绕过时钟,将 “预设 “值直接加载到触发器中。(预设值是反相的(因为在预设值和输出之间有三个反相器)。次级锁存器与之前的相同,但它提供反相和非反相输出作为反馈,允许触发器保持或切换其值。该电路说明了如何利用我们所见过的构件创建更复杂的触发器。

拨动式触发器原理图。

上图中的灰色字母与之前的多路复用器图一致,显示了三个多路复用器在芯片上的实现方式。另一个多路复用器和反相器在另一块电路中实现。我不会详细解释该电路,因为它并不说明任何新原理。

硅片中的布线:交叉外接线

由于只有一个金属层用于布线,在芯片上布线信号非常困难,需要仔细规划。即便如此,在某些情况下,一个信号必须与另一个信号交叉。这可以通过使用硅来实现 “交叉底座”,让信号从金属布线下方通过。由于硅的电阻比金属高得多,除非必要,否则应避免使用这种交叉底线。此外,交叉底座还需要额外的芯片空间。

模具上的三个十字底座

上图显示了三个交叉基底。在每个交叉底座中,信号主要在金属层中传输,但有一个信号通过掺杂硅区域(显示为绿色)从金属下穿过。第一个交叉分线器只是让一个信号从第二个信号下方穿过。第二张图片显示的是信号分支以及在两个信号下方交叉。第三张图片显示的是将一个水平信号分配到芯片上半部分和下半部分的跨底,同时在多个水平信号下方交叉。请注意连接绿色硅区域和水平金属线的椭圆形小触点。人们很容易忽略这个小触点,以为垂直信号只是在水平信号下方交叉,而不是分支。

关于芯片

本文的重点是 CMOS 逆向工程流程,而不是这款特定的芯片,但我还是要介绍一下这款芯片的信息。芯片顶部有西里尔字母 ИЕ11 表明芯片是 К561ИЕ11 或 К564ИЕ1112 。该系统比美国的半随机部件编号系统更有用。在这种零件编号中,5 表示单片集成电路,61 或 64 表示系列,特别是 4000 系列 CMOS 逻辑的商业级或军用级克隆。字符 И 表示数字电路,而 ИЕ 是计数器。因此,零件编号系统地表示该集成电路是 CMOS 计数器。

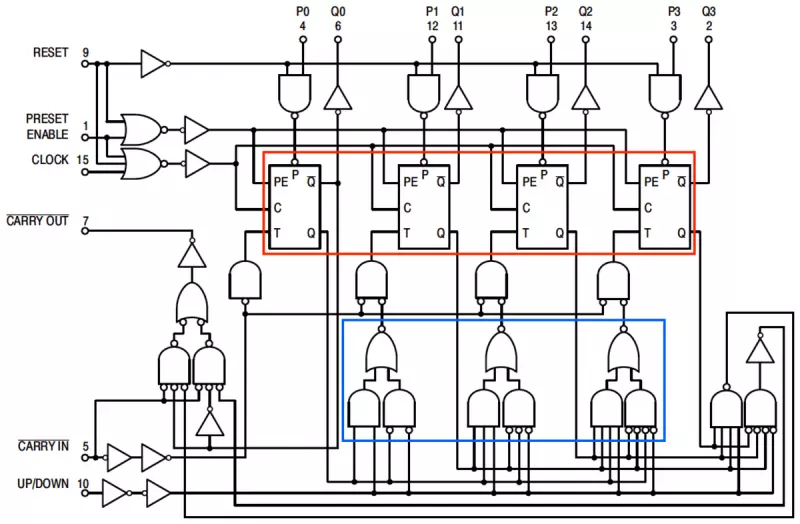

561ИЕ11 原来是摩托罗拉 MC14516 二进制上/下计数器的复制品13 。我就不详细解释原理图了,但快速浏览一下可能会有所帮助。该芯片是一个可向上或向下计数的四位计数器,其核心是四个拨动触发器(红色)。向上计数时,如果低位有进位,则触发触发器;向下计数时,如果低位有借位,则触发触发器。(底部的 AND/NOR 门(蓝色)看起来很复杂,但它们只是产生切换信号 T:如果低位全为 1,则触发触发,如果低位全为 0,则触发触发,如果低位全为 0,则触发触发。触发器还可以从 P 输入端并行加载。附加逻辑允许芯片级联,形成任意大的计数器;一个芯片的输出引脚与下一个芯片的输入引脚相连。

MC14516 上/下计数器芯片的逻辑图,摘自数据手册。

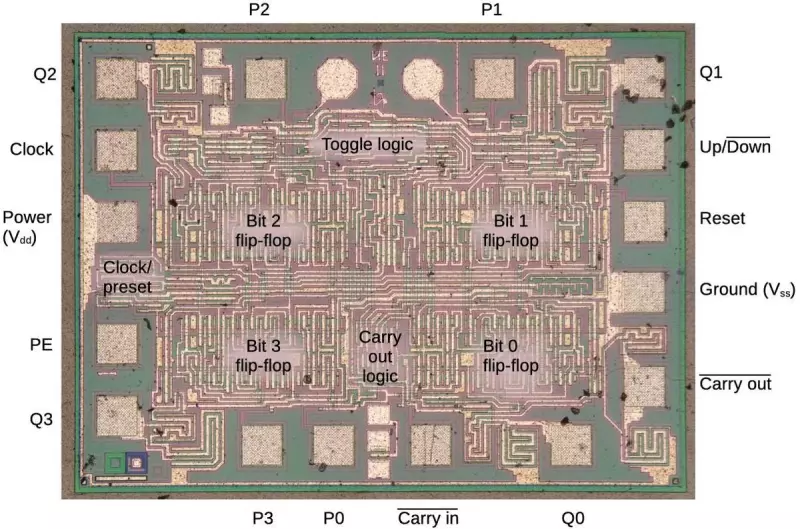

我在下面的芯片照片上标注了引脚功能和功能块。芯片的每个象限以大致对称的方式处理计数器的一个位。这种象限布局考虑到了引脚排列,否则就会显得半随机,一边是 3 位和 0 位,另一边是 2 位和 1 位,输入和输出引脚混杂在一起。拨动和携带逻辑被挤压在芯片的顶部和中部。您可能会认出每个输出引脚旁边的大型反相器。逆向工程时,寻找焊盘旁边的大型晶体管,以确定哪些引脚是输出引脚。

标有引脚和功能块的芯片。

结论

本文讨论了 CMOS 芯片中的基本电路。虽然计数器芯片古老而简单,但后来的芯片都采用了相同的原理。后期芯片的一个重要变化是引入了硅栅晶体管,这种晶体管使用多晶硅作为晶体管栅极和额外的布线层。电路是一样的,但你需要能够识别多晶硅层。许多芯片都有不止一个金属层,这就很难弄清布线连接。最后,当特征尺寸接近光的波长时,光学显微镜就会失灵。因此,这些逆向工程技术只能在一定程度上实用。尽管如此,许多有趣的 CMOS 芯片还是可以研究和逆向工程的。

如需了解更多信息,请在 Twitter @kenshirriff 或 RSS 上关注我的更新。我也是 Mastodon 上的 @kenshirriff@oldbytes.space。感谢 Martin Evtimov 提供芯片照片。

注释和参考资料

- 我不确定芯片的生产日期和生产地点。我认为这种设计很古老,来自苏联。(摩托罗拉公司在 1972 年左右推出了 MC14516,但我不知道它是何时被仿制的)。据说晶圆是一家乌克兰制造商的废料,因此可能是最近生产的。晶粒上有一个符号,可能是生产标志,但 Twitter 上没有人能辨认出来。

出现在芯片上的符号。

出现在芯片上的符号。 - 有关该芯片的更多信息,可在此处下载俄罗斯数据库;见第 5 卷第 501 页。

- 早期的 CMOS 微处理器包括 8 位 RCA 1802 COSMAC(1974 年)和 12 位 Intersil 6100(1974 年)。据说 1802 是第一个 CMOS 微处理器。主流微处理器直到 20 世纪 80 年代中期才转用 CMOS。

- 本文中的芯片采用金属栅极晶体管,铝构成晶体管栅极。这些晶体管不如 20 世纪 60 年代末开发的硅门晶体管先进。硅栅极技术在几个方面要好得多。首先,硅栅极晶体管更小、更快、更可靠,使用的电压也更低。其次,硅栅极芯片除了金属布线外,还有一层多晶硅布线;这使得芯片布局的密度增加了一倍。

- 要生产 N 型硅,需要在硅中掺入少量磷或砷等元素。在元素周期表中,这些元素在硅的右边一列,因此它们有一个 “额外 “电子。自由电子在硅中移动,携带电荷。由于电子为负,这种硅被称为 N 型硅。相反,要生产 P 型硅,则需要在硅中掺入少量的硼等元素。由于硼在元素周期表中比硅靠左一列,因此它的自由电子数比硅少一个。半导体物理学的一个奇怪之处在于,缺少的电子(称为空穴)可以像电子一样在硅中移动,但携带正电荷。由于载流子是正电荷,因此这种硅被称为 P 型硅。由于各种原因,电子比空穴更能携带电荷,因此 NMOS 晶体管比 PMOS 晶体管工作得更好。因此,PMOS 晶体管的尺寸大约是同类 NMOS 晶体管的两倍。这一怪癖对逆向工程非常有用,因为它有助于区分 NMOS 和 PMOS 晶体管。所需的掺杂量可能少得离谱,在某些情况下,每十亿个硅原子中需要掺杂 20 个硼原子。N 型硅的典型掺杂水平是每立方厘米 1015 个磷或砷原子,这听起来似乎很多,直到你意识到纯硅由每立方厘米5×1022 个原子组成。重度掺杂的 P+ 区域每立方厘米可能有 1020 个掺杂原子,即每 500 个硅原子掺杂一个硼原子。(此处对掺杂水平进行了描述)。

- 该芯片是在 N 型硅衬底上制作的,并在 NMOS 晶体管上设置了 P 型硅孔。芯片也可以反过来制作,从 P 型硅开始,为 PMOS 晶体管设置 N 型硅孔。另一种方法是 “双阱 “CMOS 工艺,为 NMOS 和 PMOS 晶体管建造阱。

- 体硅电压使晶体管与体硅之间的边界成为反向偏压二极管,因此电流无法流过边界。具体来说,对于 PMOS 晶体管,N 硅衬底与正电源相连。对于 NMOS 晶体管,P 硅层与地相连。P-N 结就像一个二极管,电流从 P 流向 N。其结果是,硅块可被视为绝缘体,电流被限制在 N+ 和 P+ 掺杂区域。如果反向偏压发生逆转,例如由于电源波动,电流就会流过衬底。这可能会导致 “闩锁”,即 N 和 P 区充当寄生 NPN 和 PNP 晶体管,闩锁进入 “导通 “状态。这将导致电源和地线短路,并可能毁坏芯片。关键是,基底电压对芯片的正常运行非常重要。

- 该芯片中的许多反相器重复使用晶体管,以增加电流输出。使用栅极宽度两倍的单晶体管也能达到同样的效果(即图中高度的两倍)。(由于这些晶体管排列成行,如果将晶体管高度增加一倍,就会破坏布局,因此使用更多晶体管而不是改变尺寸是合理的。

- 有些芯片使用动态逻辑,在这种情况下,可以让栅极浮动,既不拉高也不拉低。由于栅极电阻极高,栅极电容会在短时间内保持其值(0 或 1)。几毫秒后,电荷就会泄漏,因此动态逻辑必须在信号衰减之前不断刷新信号。

- 一般来说,CMOS 电路的输入端不需要中间电压的原因是,中间电压可能会导致 PMOS 晶体管部分导通,同时 NMOS 晶体管也部分导通。其结果是,从电源到地的大电流会通过晶体管。

- 芯片上的一个复杂逻辑门与我预期的实现方式不符。特别是,对于某些输入,输出既不是高电平也不是低电平。追踪这些输入的源头就能发现问题所在:该逻辑门同时将信号及其补码作为输入。因此,一些 “理论 “输入是不可能的;这些输入不可能既是高电平又是低电平。逻辑门经过优化,可以忽略这些情况,从而简化了实现过程。

- 本原理图解释了芯片上 3 输入 NOR 逻辑门的物理布局,以防接线不清楚。请注意,PMOS 晶体管是串联的,而 NMOS 晶体管是并联的,尽管这两种类型的晶体管在物理上都是成行排列的。

芯片上的 3 输入 NOR 门。该原理图与物理布局相匹配。 - 商业级芯片和军用级芯片可能使用相同的芯片,但通过测试级别加以区分。因此,我们无法将芯片分为 561 系列和 564 系列。

- 摩托罗拉于 1971 年推出 MC14500 系列,以填补 CD4000 系列的空白。有关该系列的更多信息,请参阅 “对互补 MOS 的坚定承诺”。

本文文字及图片出自 Reverse engineering CMOS, illustrated with a vintage Soviet counter chip